Scan(扫描测试)和BIST(内建自测试)都是用于芯片测试的技术,但它们在实现方式和应用场景上有所不同。

**Scan(扫描测试)**:

扫描测试是一种常用的数字集成电路测试技术。在设计阶段,工程师会在芯片中添加额外的硬件(扫描链),以便在测试阶段将测试数据输入到芯片内部的特定位置,并从特定位置读取测试结果。扫描测试主要用于生产阶段的测试,以检测出可能的制造缺陷。它可以提供很高的故障覆盖率,但是需要外部的测试设备和复杂的测试向量生成。

**BIST(内建自测试)**:

BIST是一种将测试逻辑直接集成到被测试系统中的方法,使系统能够进行自我测试。BIST通常包括一个测试模式生成器和一个测试响应分析器。在测试阶段,测试模式生成器会自动产生测试向量,测试响应分析器会收集并分析测试结果。BIST可以在系统的生命周期中的任何时间进行测试,包括生产测试、系统启动时的自我测试,甚至系统运行时的在线测试。BIST的优点是可以进行在系统级别的测试,无需外部的测试设备,但可能会增加设计的复杂性和硬件开销。

Scan Design -- 扫描路径设计

Scan 技术最初由Kobayashi等人提出来的,它的优点是基本原理是时序电路可以模型化为一个组合电路网络。

Scan design的设计目标是能够提高可控性和可观测性。

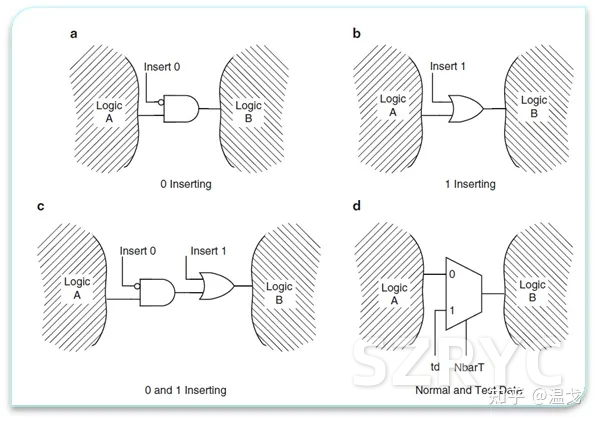

通过在逻辑A和逻辑B之间插入一些额外的硬件电路,便可观测&控制逻辑A传递到逻辑B的值。[1]

scan 分为两步:

1. Scan replacement

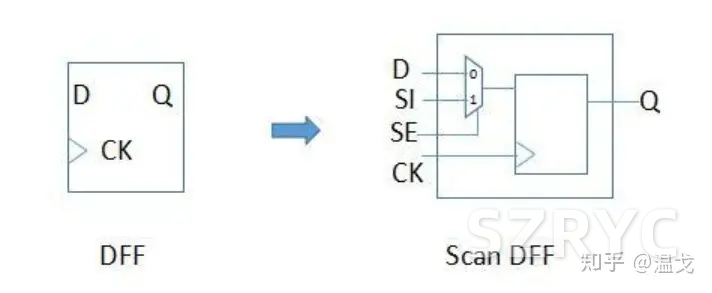

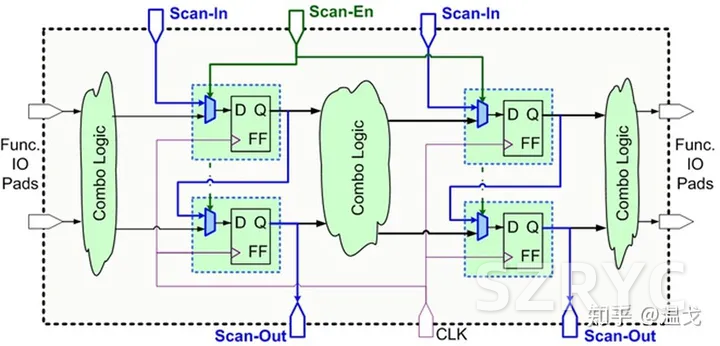

把普通的DFF,替换成带Scan DFF,下图是一个mux-D的DFF,可以看到多了一个SI,SE,和一个mux。

其SE端值为0时,电路工作在正常功能状态并能把D端的值锁存下来;当SE为1时,电路工作在所谓scan mode并锁存SI的值。

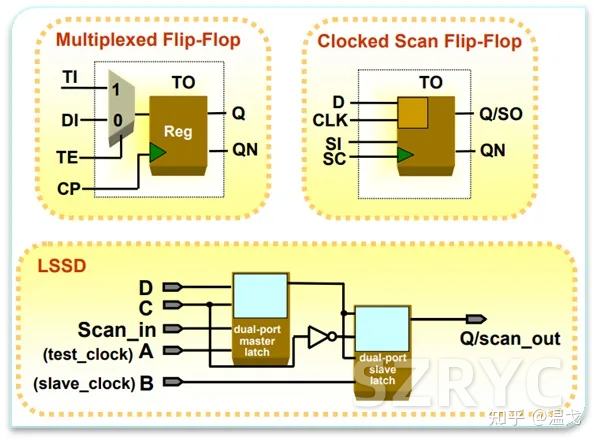

常见的scan cell有三种:

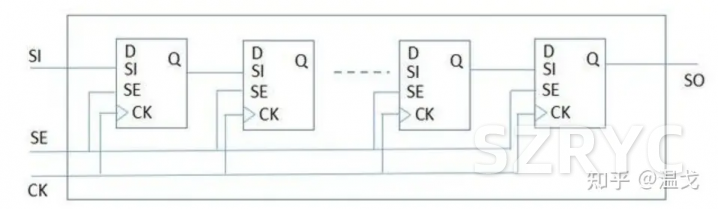

2. Scan stitching

Scan stitching 是把上一步中得到的Scan DFF的Q和SI连接在一起形成scan chain。在芯片的顶层有全局的SE信号,以及scan chain的输入输出信号:SI 和 SO。通过scan chain的连续动作,就可以把问题从对复杂时序电路的测试转化成测试组合电路。

实际在设计中,这两步都是由EDA工具完成的。

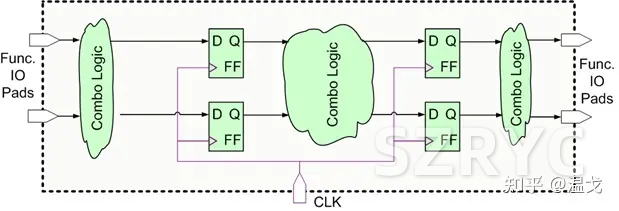

上面的两幅图都只有时序单元,我们再把组合逻辑放进来。

Before scan

After scan insertion

Scan test 的步骤:

1.把Scan-En设成0,此时电路工作在正常状态(function mode)下, scan insertion对电路的正常功能没有影响。

2.把Scan-En设成1,然后把enable clock来驱动寄存器,在Scan-In端输入测试数据,然后在输出端Scan-Out观测,用此种方法便可以测试Flip-Flop.

3.测试组合逻辑的时候,把Scan-En设成1,然后enable clock来驱动寄存器,在Scan-In端输入测试数据,两个时钟周期后,数据便会送到组合逻辑的输入端。

4.然后把Scan-En设成0,时钟打一拍,经过组合逻辑的输出值便会送到右侧的寄存器中。

5.再把Scan-En设成1,此时scan chain 工作在shift mode,此时便可以把组合逻辑的输出值shift出来,和期望值进行比较。

经过这样一个周期,图中的组合逻辑和时序逻辑便都被测试到了。

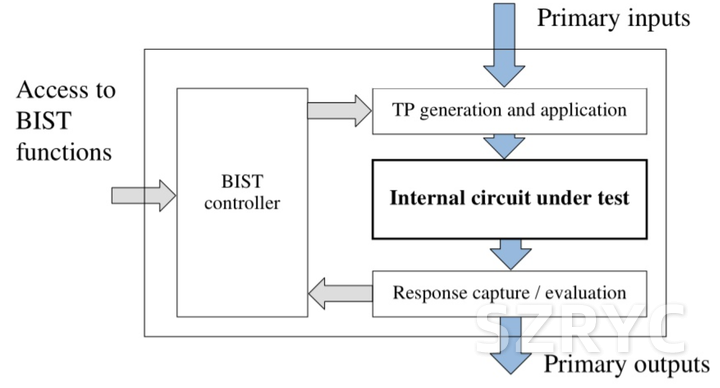

BIST -- 内建自测试

内建自测试(BIST)设计技术通过在芯片的设计中加入一些额外的自测试电路,测试时只需要从外部施加必要的控制信号,通过运行内建的自测试硬件和软件,检查被测电路的缺陷或故障。和扫描设计不同的是,内建自测试的测试向量一般是内部生成的,而不是外部输入的。内建自测试可以简化测试步骤,而且无需昂贵的测试仪器和设备(如ATE设备),但它增加了芯片设计的复杂性。

BIST大致可分为两类:Logic BIST(LBIST) 和 Memory BIST (MBIST)

LBIST通常用于测试随机逻辑电路,一般采用一个伪随机测试图形生成器来产生输入测试图形,应用于器件内部机制;而采用多输入寄存器(MISR)作为获得输出信号产生器。MBIST只用于存储器测试,典型的MBIST包含测试电路用于加载,读取和比较测试图形。目前存在几种业界通用的MBIST算法,比如“March”,March-C,MATS+算法。

另一种比较少见的BIST称为Array BIST,它是MBIST的一种,专门用于嵌入式存储器的自我测试。Analog BIST,则用于模拟电路的自我测试。 BIST技术正成为高价ATE的替代方案,但是BIST技术目前还无法完全取代ATE,他们将在未来很长一段时间内共存。

Scan和BIST是芯片可测性设计中两种非常重要的技术,也是一个DFT工程师必备的技能。