5、小外形封装(SOP)

SOP(Small Out-Line Package)是表面贴装型封装之一,也称之为SOL或DFP,引脚从封装两侧引出呈海鸥翼状(L字形)。材料有塑料和陶瓷两种。

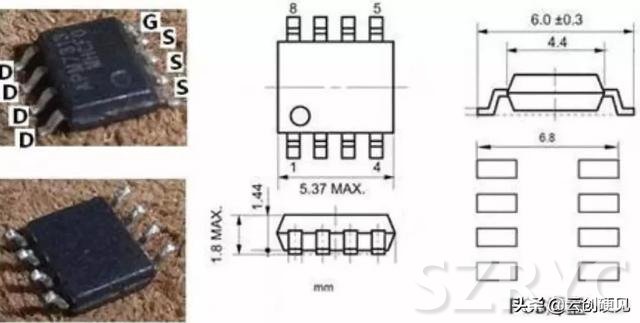

SOP封装标准有SOP-8、SOP-16、SOP-20、SOP-28等,SOP后面的数字表示引脚数。MOSFET的SOP封装多数采用SOP-8规格,业界往往把“P”省略,简写为SO(Small Out-Line)。

SOP-8封装尺寸

SO-8为PHILIP公司率先开发,采用塑料封装,没有散热底板,散热不良,一般用于小功率MOSFET。

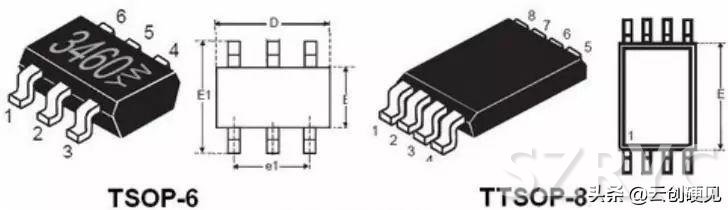

后逐渐派生出TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)等标准规格;其中TSOP和TSSOP常用于MOSFET封装。

常用于MOS管的SOP派生规格

6、方形扁平式封装(QFP)

QFP(Plastic Quad Flat Package)封装的芯片引脚之间距离很小,管脚很细,一般在大规模或超大型集成电路中采用,其引脚数一般在100个以上。

用这种形式封装的芯片必须采用SMT表面安装技术将芯片与主板焊接起来。该封装方式具有四大特点:

①适用于SMD表面安装技术在PCB电路板上安装布线;

②适合高频使用;

③操作方便,可靠性高;

④芯片面积与封装面积之间的比值较小。

与PGA封装方式一样,该封装方式将芯片包裹在塑封体内,无法将芯片工作时产生的热量及时导出,制约了MOSFET性能的提升;而且塑封本身增加了器件尺寸,不符合半导体向轻、薄、短、小方向发展的要求;另外,此类封装方式是基于单颗芯片进行,存在生产效率低、封装成本高的问题。

因此,QFP更适于微处理器/门陈列等数字逻辑LSI电路采用,也适于VTR信号处理、音响信号处理等模拟LSI电路产品封装。

7、四边无引线扁平封装(QFN)

QFN(Quad Flat Non-leaded package)封装四边配置有电极接点,由于无引线,贴装表现出面积比QFP小、高度比QFP低的特点;其中陶瓷QFN也称为LCC(Leadless Chip Carriers),采用玻璃环氧树脂印刷基板基材的低成本塑料QFN则称为塑料LCC、PCLC、P-LCC等。

是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴表面贴装芯片封装技术。

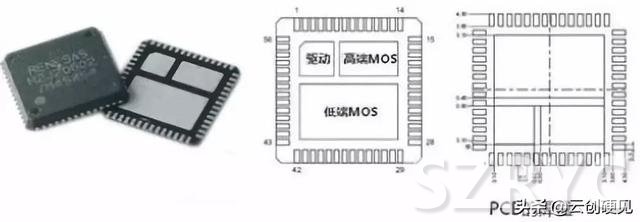

QFN主要用于集成电路封装,MOSFET不会采用。不过因Intel提出整合驱动与MOSFET方案,而推出了采用QFN-56封装(“56”指芯片背面有56个连接Pin)的DrMOS。

需要说明的是,QFN封装与超薄小外形封装(TSSOP)具有相同的外引线配置,而其尺寸却比TSSOP的小62%。根据QFN建模数据,其热性能比TSSOP封装提高了55%,电性能(电感和电容)比TSSOP封装分别提高了60%和30%。最大的缺点则是返修难度高。

采用QFN-56封装的DrMOS

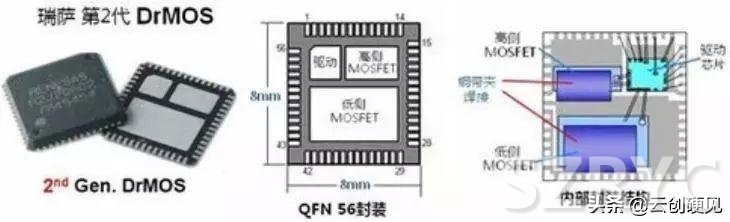

随着技术的革新与进步,把驱动器和MOSFET整合在一起,构建多芯片模块已经成为了现实,这种整合方式同时可以节省相当可观的空间从而提升功耗密度,通过对驱动器和MOS管的优化提高电能效率和优质DC电流,这就是整合驱动IC的DrMOS。

瑞萨第2代DrMOS

经过QFN-56无脚封装,让DrMOS热阻抗很低;借助内部引线键合以及铜夹带设计,可最大程度减少外部PCB布线,从而降低电感和电阻。

另外,采用的深沟道硅(trench silicon)MOSFET工艺,还能显著降低传导、开关和栅极电荷损耗;并能兼容多种控制器,可实现不同的工作模式,支持主动相变换模式APS(Auto Phase Switching)。

除了QFN封装外,双边扁平无引脚封装(DFN)也是一种新的电子封装工艺,在安森美的各种元器件中得到了广泛采用,与QFN相比,DFN少了两边的引出电极。

8、塑封有引线芯片载体(PLCC)

PLCC(Plastic Quad Flat Package)外形呈正方形,尺寸比DIP封装小得多,有32个引脚,四周都有管脚,引脚从封装的四个侧面引出,呈丁字形,是塑料制品。

其引脚中心距1.27mm,引脚数从18到84不等,J形引脚不易变形,比QFP容易操作,但焊接后的外观检查较为困难。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。

PLCC封装是比较常见,用于逻辑LSI、DLD(或程逻辑器件)等电路,主板BIOS常采用的这种封装形式,不过目前在MOS管中较少见。

PLCC封装样式

主流企业的封装与改进

由于CPU的低电压、大电流的发展趋势,对MOSFET提出输出电流大,导通电阻低,发热量低散热快,体积小的要求。MOSFET厂商除了改进芯片生产技术和工艺外,也不断改进封装技术,在与标准外形规格兼容的基础上,提出新的封装外形,并为自己研发的新封装注册商标名称。

1、瑞萨(RENESAS)WPAK、LFPAK和LFPAK-I封装

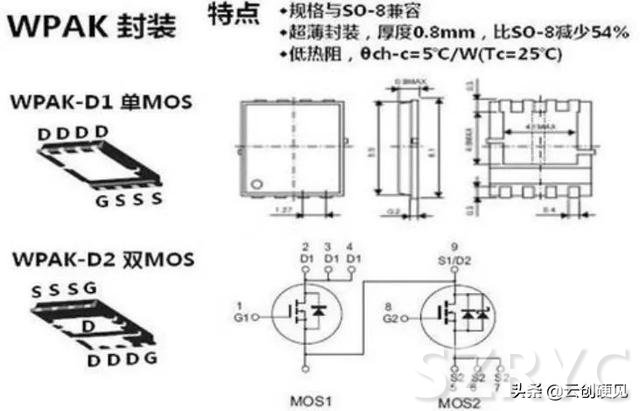

WPAK是瑞萨开发的一种高热辐射封装,通过仿D-PAK封装那样把芯片散热板焊接在主板上,通过主板散热,使小形封装的WPAK也可以达到D-PAK的输出电流。WPAK-D2封装了高/低2颗MOSFET,减小布线电感。

瑞萨WPAK封装尺寸

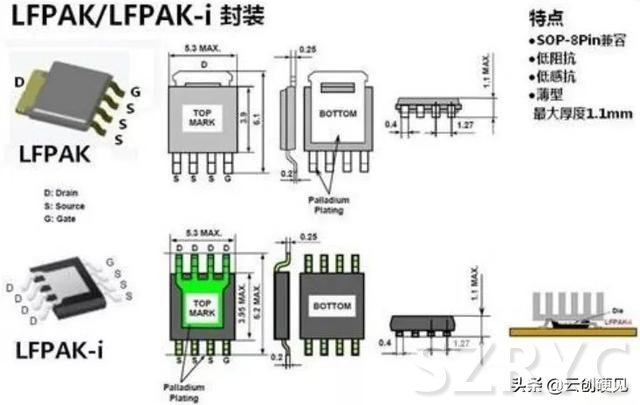

LFPAK和LFPAK-I是瑞萨开发的另外2种与SO-8兼容的小形封装。LFPAK类似D-PAK,但比D-PAK体积小。LFPAK-i是将散热板向上,通过散热片散热。

瑞萨LFPAK和LFPAK-I封装

2、威世(Vishay)Power-PAK和Polar-PAK封装

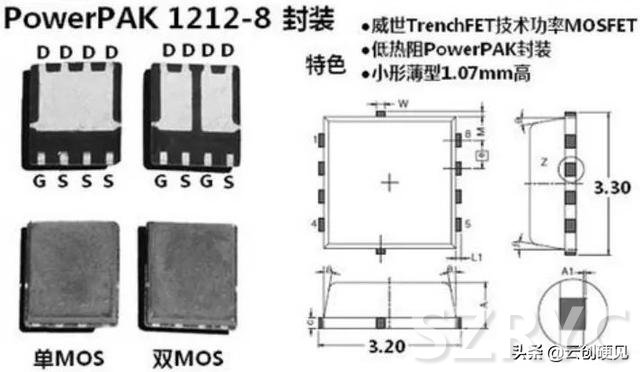

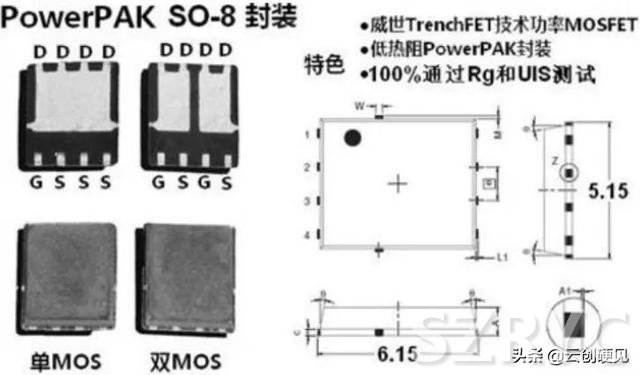

Power-PAK是威世公司注册的MOSFET封装名称。Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8两种规格。

威世Power-PAK1212-8封装

威世Power-PAK SO-8封装

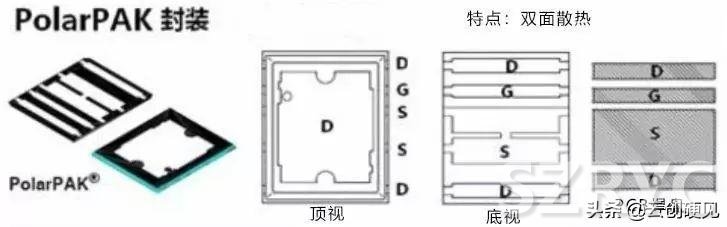

Polar PAK是双面散热的小形封装,也是威世核心封装技术之一。Polar PAK与普通的so-8封装相同,其在封装的上、下两面均设计了散热点,封装内部不易蓄热,能够将工作电流的电流密度提高至SO-8的2倍。目前威世已向意法半导体公司提供Polar PAK技术授权。

威世Polar PAK封装

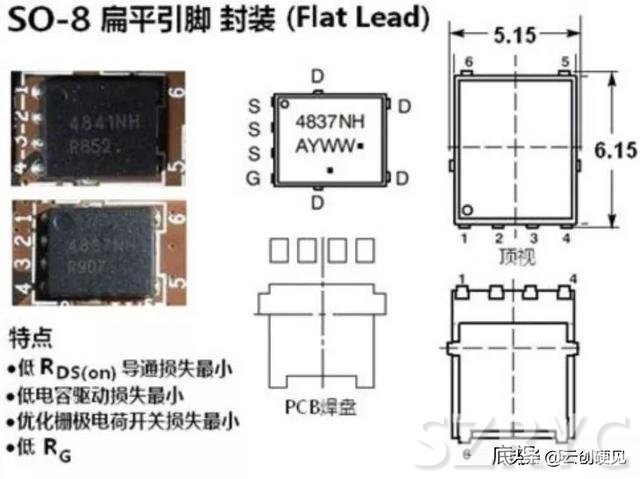

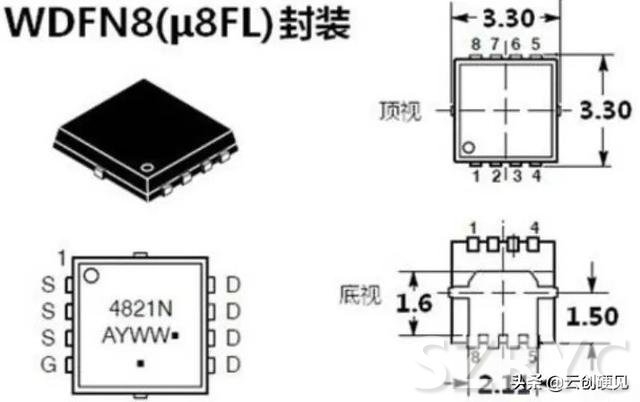

3、安森美(Onsemi)SO-8和WDFN8扁平引脚(Flat Lead)封装

安美森半导体开发了2种扁平引脚的MOSFET,其中SO-8兼容的扁平引脚被很多板卡采用。安森美新近推出的NVMx和NVTx功率MOSFET就采用了紧凑型DFN5(SO-8FL)和WDFN8封装,可最大限度地降低导通损耗,另外还具有低QG和电容,可将驱动器损耗降到最低的特性。

安森美SO-8扁平引脚封装

安森美WDFN8封装

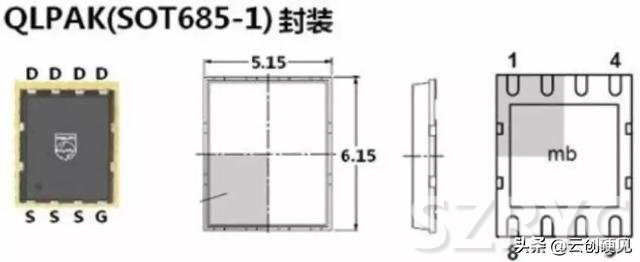

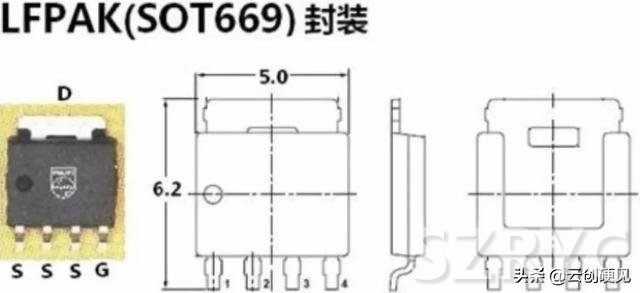

4、恩智浦(NXP)LFPAK和QLPAK封装

恩智浦(原Philps)对SO-8封装技术改进为LFPAK和QLPAK。其中LFPAK被认为是世界上高度可靠的功率SO-8封装;而QLPAK具有体积小、散热效率更高的特点,与普通SO-8相比,QLPAK占用PCB板的面积为6*5mm,同时热阻为1.5k/W。

恩智浦LFPAK封装

恩智浦QLPAK封装